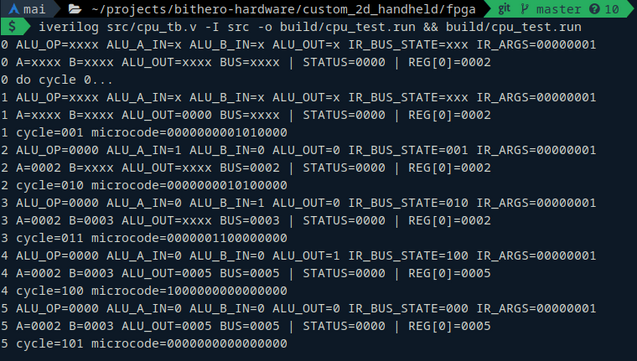

so far there's just one thing that drives me mad about

#VHDL, or maybe specifically it's implementation in

#Vivado:

if I name a component not exactly as the entity and forget to add corresponding configuration, it simply won't create the instance in the architecture and won't connect the signal, and issue no error whatsoever, just silently continue as if nothing happened

and then if I add the configuration, it still refuses to pick it up and doesn't create the instance

this ought to be a bug, should try it on

#GHDL perhaps

in other respects it's pretty nice to write in, at first there are more, sometimes silly, errors (like you have gazillion of types which all are essentially a bit vector¹, and the type-checker will fuck with you if you aren't properly converting one into the other), and there are much fewer syntactic constructs than in

#Verilog, let alone

#SystemVerilog, that you're forced to wrap it all properly, but then, if it works, it works correctly, the way you intended

I pretty much want to try and use

#Ada for a firmware, and I don't care if the tool-chain is proprietary (is

#GNAT proprietary?) — the FLOSS enthusiasts should adopt better standards if they want me to use their stuff and contribute more

¹ boolean, bit, std_logic for single bit; arrays thereof; std_logic_vector, signed, unsigned, integer, natural, positive, time, and real are all mutually incompatible, modulo few exceptions

if-then-else only works with booleans, you can't just put a value of std_logic in place of the condition